•

Menjelaskan Transistor-Transistor Logic

(TTL)

•

Melakukan simulasi rangkaian Transistor

Transistor Logic (TTL)

a. Power supply

Power supply atay catu daya adalah suatu alat listrik yang dapat menyediakan energi listrik untuk perangkat listrik maupun elektronika lainnya.

b. Voltmeter

Voltmeter adalah alat ukur yang digunakan untuk mengukur tegangan listrik dalam sebuah rangkaian.

3. Amperemeter

a. Resistor

Resistor merupakan komponen elektronika pasif yang berfungsi untuk membatasi arus yang mengalir pada suatu rangkaian dan berfungsi sebagai terminal antara dua komponen elektronika. Tegangan pada suatu resistor sebanding dengan arus yang melewatinya.

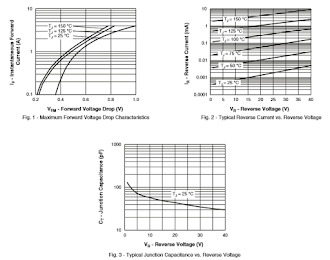

Spesifikasi:

Grafik:

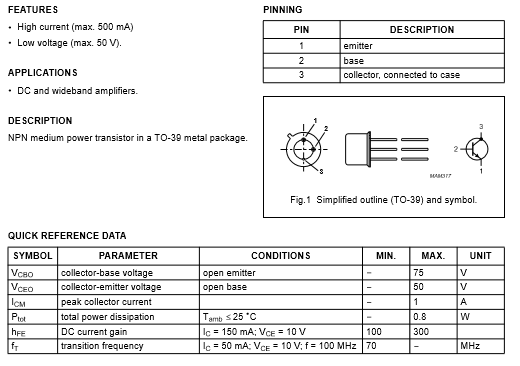

b. Transistor NPN (BC547)

Transistor merupakan alat semikonduktor yang dapat digunakan sebagai penguat sinyal, pemutus atau penyambung sinyal (switching), stabilisasi tegangan, dan fungsi lainnya. Transistor memiliki 3 kaki yaitu basis, kolektor, dan emitter.

Fitur:

1. DC Current gain (hfe) maksimal 800

2. Arus Collector kontinu (Ic) 100mA

3. Tegangan Base-Emitter (Vbe) 6V

4. Arus Base (Ib) maksimal 5mA

Spesifikasi:

Konfigurasi pin:

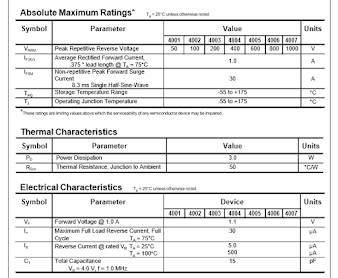

Dioda adalah komponen elektronika yang terdiri dari dua kutub dan berfungsi menyearahkan arus. Komponen ini terdiri dari penggabungan dua semikonduktor yang masing-masing diberi doping (penambahan material) yang berbeda, dan tambahan material konduktor untuk mengalirkan listrik.

3. Arus balik 5uA

4. Tegangan balik RMS 35V

5. Tegangan balik repetitif 50V

2. Tegangan drop 0.49V

3. Tegangan balik 40V

Gerbang NAND menghendaki semua inputnya bernilai 0 (terhubung dengan ground) atau salah satunya bernilai 1 agar menghasilkan output yang berharga 1.

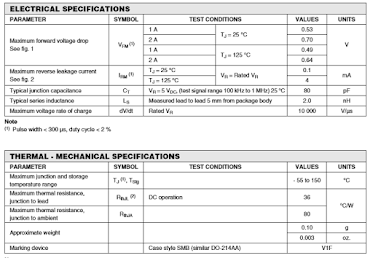

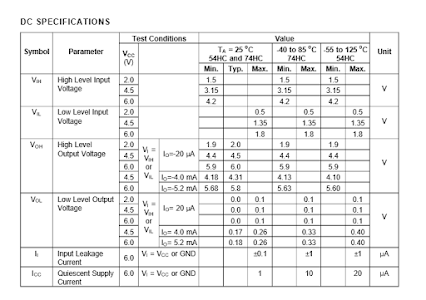

Spesifikasi:

Konfigurasi pin:

e. Gerbang logika AND (IC 7411)

Gerbang AND (IC 4081) memerlukan 2 atau lebih Masukan (Input)

untuk menghasilkan hanya 1 Keluaran (Output). Gerbang AND akan menghasilkan

Keluaran (Output) Logika 1 jika semua masukan (Input) bernilai Logika 1 dan

akan menghasilkan Keluaran (Output) Logika 0 jika salah satu dari masukan

(Input) bernilai Logika 0.

Spesifikasi:

Konfigurasi pin:

f. Gerbang Logika OR (IC 74HC4075)

OR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila salah satu, sebagian atau semua inputnya berlogika 1.

Spesifikasi:

Konfigurasi pin:

g. Gerbang logika NOR (IC 7427)

NOR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 1 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 0.

Spesifikasi:

|

Supply Voltage |

7V |

|

Input Voltage |

5.5V |

|

Operating Free Air Temperature |

0°C to +70°C |

|

Storage Temperature Range |

-65°C to +150°C |

Konfigurasi pin:

TTL sebagaimana diuraikan di atas adalah singkatan dari transistor transistor logic. Ini adalah keluarga logika yang diimplementasikan dengan teknologi proses bipolar yang menggabungkan atau mengintegrasikan transistor NPN, dioda persimpangan PN, dan resistor tersebar dalam satu struktur monolitik untuk mendapatkan fungsi logika yang diinginkan. Gerbang NAND adalah blok bangunan dasar dari keluarga logika ini. Subfamili berbeda dalam keluarga logika ini, seperti yang diuraikan sebelumnya, termasuk TTL standar, TTL daya rendah, TTL daya tinggi, TTL Schottky daya rendah, TTL Schottky daya rendah, TTL Schottky daya rendah lanjutan, TTL Schottky canggih, dan TTL cepat.

5.3.1 TTL Standar

5.3.1.1 Operasi Rangkaian

5.3.1.2 Tahap Keluaran Tiang

Totem

Transistor Q3 dan Q4

membentuk apa yang dikenal sebagai pengaturan keluaran kutub-totem. Dalam

pengaturan seperti itu, baik Q3 atau Q4 berjalan pada suatu waktu tergantung

pada status logika input. Itu pengaturan tiang totem pada keluaran memiliki

keuntungan berbeda tertentu. Keuntungan utama menggunakan koneksi tiang-totem

adalah ia menawarkan impedansi keluaran rendah di kedua keluaran HIGH dan LOW.

Dalam status HIGH, Q3 bertindak sebagai pengikut emitor dan memiliki impedansi

keluaran sekitar 70. Dalam kondisi LOW, Q4 jenuh dan impedansi keluaran

kira-kira 10. Karena impedansi keluaran rendah, setiap kapasitansi yang

menyimpang pada keluaran dapat diisi atau dikosongkan dengan sangat cepat melalui

impedansi rendah ini, sehingga memungkinkan transisi cepat pada keluaran dari

satu keadaan ke keadaan lainnya.

Keuntungan lain adalah, ketika output dalam keadaan logika LOW, transistor Q4 perlu mengalirkan arus yang cukup besar jika kolektornya diikat ke VCC melalui R3 saja. Sebuah nonconducting Q3 mengatasi masalah ini. Kerugian dari hasil konfigurasi keluaran tiang totem dari tindakan mematikan Q4 menjadi lebih lambat daripada tindakan sakelar Q3. Karena ini, akan ada sebagian kecil waktu, dari urutan beberapa nanodetik, ketika kedua transistor melakukan, sehingga menarik arus deras dari suplai

5.3.1.3 Fitur

Karakteristik

Singkatnya, parameter karakteristik dan fitur keluarga perangkat TTL standar termasuk yang berikut ini: VIL = 0,8 V; VIH = 2 V; IIH = 40 A; IIL = 1,6 mA; VOH = 2,4 V; VOL = 0,4 V; IOH = 400 A; IOL = 16 mA; VCC = 4,75–5,25 V (74-series) dan 4,5–5,5 V (54-series); perambatan penundaan (untuk resistansi beban 400, kapasitansi beban 15 pF dan suhu lingkungan dari 25 ° C) = 22 ns (maks.) untuk transisi LOW-to-HIGH pada keluaran dan 15 ns (maks.) untuk transisi keluaran HIGH ke LOW; margin kebisingan kasus terburuk = 0,4 V; fan-out = 10; ICCH (untuk keempat gerbang) = 8 mA; ICCL (untuk keempat gerbang) = 22 mA; kisaran suhu operasi = 0–70 ° C (74-seri) dan −55 hingga +125 ° C (seri 54); kecepatan – produk daya = 100 pJ; toggle flip-flop maksimum frekuensi = 35 MHz.

5.3.2 Gerbang Logika

Lain dalam TTL Standar

Seperti diuraikan sebelumnya, gerbang NAND adalah blok bangunan fundamental dari keluarga TTL.

5.3.2.1 NOT Gate (atau

Inverter)

5.3.2.2 Gerbang NOR

Gambar 5.9 menunjukkan skema internal gerbang NOR dalam keluarga TTL standar. Skema yang ditunjukkan adalah salah satu dari empat gerbang NOR dalam gerbang NOR empat masukan dua (tipe 7402/5402). Disisi input ada dua transistor terpisah sebagai pengganti transistor multi-emitor dari gerbang NAND. Input diumpankan ke pemancar dari dua transistor, kolektor yang lagi-lagi memberi makan basis dua transistor dengan terminal kolektor dan emitor diikat menjadi satu. Nilai resistansi yang digunakan sama dengan yang digunakan dalam kasus gerbang NAND. Tahap keluaran juga merupakan tiang totem yang sama tahap keluaran. Sirkuitnya cukup jelas.

5.3.2.3 AND gate

5.3.2.4 OR Gate

Gambar 5.11

menunjukkan skema internal gerbang OR dalam keluarga TTL standar

5.3.2.5 EXCLUSIVE-OR

Gate

Gambar 5.12 menunjukkan skema internal gerbang EX-OR dalam keluarga TTL standar. Skema yang ditunjukkan adalah salah satu dari empat gerbang EX-OR dalam gerbang EX-OR dua input quad (tipe 7486/5486).

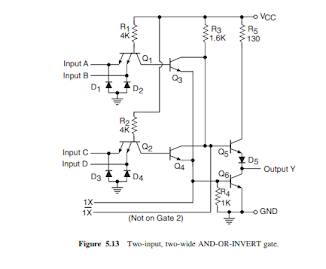

5.3.2.6 AND-OR-INVERT

Gate

Gambar 5.13 menunjukkan skema internal dari gerbang AND-OR-INVERT atau AND-NOR dua-lebar, dua input. Skema yang ditampilkan adalah salah satu dari dua gerbang dalam gerbang AND-ORINVERT dua lebar, dua input (tipe 7450/5450)

5.3.2.7 Open Collector Gate

5.3.2.8 Tristate Gate

Gerbang tristate memiliki tiga status keluaran, yaitu logika Status LOW, status logika HIGH, dan status impedansi tinggi.

5.3.3 Low-Power TTL

TTL berdaya rendah

adalah varian berdaya rendah dari TTL standar di mana disipasi daya lebih

rendah dicapai dengan mengorbankan kecepatan operasi yang berkurang.

5.3.3.1 Characteristic

Features

Ciri-ciri karakteristik keluarga ini dirangkum sebagai berikut: VIH = 2 V; VIL = 0,7 V; IIH = 10 A; IIL = 0,18 mA; VOH = 2,4 V; VOL = 0,4 V; IOH = 200 A; IOL = 3,6 mA; VCC = 4,75–5,25 V (74 seri) dan 4,5–5,5 V (seri-54); penundaan propagasi (untuk resistansi beban 4000, kapasitansi beban 50 pF, VCC = 5 V dan suhu lingkungan 25 ° C) = 60 ns (maks.) untuk LOW-to-HIGH dan transisi keluaran HIGH-ke-LOW; margin kebisingan kasus terburuk = 0,3 V; fan-out = 20; ICCH (untuk semua empat gerbang) = 0,8 mA; ICCL (untuk keempat gerbang) = 2,04 mA; kisaran suhu operasi = 0–70 ° C (74-seri) dan −55 hingga +125 ° C (seri 54); kecepatan-daya produk = 33 pJ; toggle flip-flop maksimum frekuensi = 3 MHz.

5.3.4 High-Power TTL

(74H/54H)

TTL daya tinggi adalah

varian kecepatan tinggi dan daya tinggi dari TTL standar yang meningkatkan

kecepatan (penundaan propagasi yang dikurangi) dicapai dengan mengorbankan

disipasi daya yang lebih tinggi. Gambar 5.18 menunjukkan skema internal gerbang

TTL NAND berdaya tinggi

5.3.5 Schottky TTL

(74S/54S)

Schottky TTL

menawarkan kecepatan sekitar dua kali lipat dari TTL daya tinggi untuk konsumsi

daya yang sama. Gambar 5.19 menunjukkan skema internal gerbang Schottky TTL

NAND. Sirkuit yang ditampilkan adalah salah satu dari empat gerbang di dalam

quad dua input NAND (tipe 74S00 atau 54S00).

5.3.6 Low-Power

Schottky TTL (74LS/54LS)

Schottky TTL berdaya

rendah adalah varian konsumsi daya rendah dari Schottky TTL. Gambar 5.20 menunjukkan

skema internal gerbang Schottky TTL NAND berdaya rendah. Sirkuit yang

ditunjukkan adalah dari salah satu dari empat gerbang di dalam quad dua input

NAND (tipe 74LS00 atau 54LS00).

5.3.7 Advanced

Low-Power Schottky TTL (74ALS/54ALS)

Ide dasar di balik

pengembangan daya rendah Schottky TTL (ALS-TTL) dan lanjutan Schottky TTL

(AS-TTL) yang dibahas dalam Bagian 5.3.8 lebih jauh untuk meningkatkan kedua

kecepatan dan kinerja konsumsi daya dari keluarga Schottky TTL dan Schottky TTL

berdaya rendah masing-masing. Dalam subfamili TTL yang dibahas sejauh ini, kami

telah melihat bahwa subfamili yang berbeda dicapai meningkatkan kecepatan

dengan mengorbankan peningkatan konsumsi daya, atau sebaliknya. Misalnya, TTL

daya rendah menawarkan konsumsi daya yang lebih rendah di atas TTL standar

dengan biaya pengurangan kecepatan. Itu TTL berdaya tinggi, di sisi lain,

menawarkan kecepatan yang lebih baik daripada TTL standar dengan mengorbankan peningkatan

konsumsi daya. ALS-TTL dan AS-TTL menggabungkan fitur desain sirkuit baru

tertentu dan teknologi fabrikasi untuk mencapai peningkatan kedua parameter.

Baik ALS-TTL dan AS-TTL menawarkan peningkatan dalam kecepatan-daya produk

masing-masing melalui LS-TTL dan S-TTL dengan faktor 4.

5.3.7.1 Fitur Karakteristik

Fitur karakteristik dari keluarga ini diringkas sebagai berikut: VIH = 2V, VIL = 0.8V; IIH = 20 A; IIL = 0.1mA; VOH = (VCC − 2) V; VOL = 0,5V; IOH = 0.4mA; IOL = 8mA (74ALS) dan 4mA (54ALS);

VCC = 4,5–5,5 V; penundaan propagasi (untuk resistansi beban 500, kapasitansi beban 50pF, VCC = 4.5–5.5V dan suhu lingkungan minimum hingga maksimum) = 11ns / 16ns (maks.) untuk LOW-to-HIGH dan 8ns / 13ns untuk transisi keluaran TINGGI-ke-RENDAH (74ALS / 54ALS); margin kebisingan kasus terburuk = 0,3V; fan-out = 20; ICCH (untuk keempat gerbang) = 0.85mA; ICCL (untuk keempat gerbang) = 3mA; kisaran suhu pengoperasian = 0–70 ° C (74 seri) dan −55 hingga + 125 ° C (54 seri); kecepatan – daya produk = 4.8pJ; frekuensi sakelar flip-flop maksimum = 70MHz.5.3.8 Advanced

Schottky TTL (74AS/54AS)

Gambar 5.22

menunjukkan skema internal gerbang Schottky TTL NAND tingkat lanjut. Sirkuit

ditampilkan adalah salah satu dari empat gerbang di dalam quad dua input NAND

(tipe 74AS00 atau 54AS00).

5.3.8 Advanced Schottky TTL (74AS/54AS

5.3.8.1 Fitur KarakteristikFitur karakteristik khas keluarga ini diringkas sebagai berikut: VIH = 2V, VIL = 0.8V; IIH = 20 A; IIL = 0,5mA; VOH = (VCC − 2) V; VOL = 0,5V; IOH = 2mA; IOL = 20mA; VCC = 4,5–5,5V; penundaan propagasi (untuk resistansi beban 50, kapasitansi beban 50pF, VCC = 4,5–5,5V dan suhu lingkungan minimum hingga maksimum) = 4,5ns / 5ns (maks.) Untuk LOW -to-HIGH dan 4ns / 5ns (maks.) untuk transisi output HIGH-to-LOW (74AS / 54AS); margin kebisingan kasus terburuk = 0,3V; fan-out = 40; ICCH (untuk semua kota) = 3.2mA; ICCL (forallfourgates) = 17.4mA; rentang suhu operasi = 0–70 ° C (74-series) dan − 55 to + 125 ° C (54-series); kecepatan – daya produk = 13.6pJ; frekuensi toggle flip-flop maksimum = 200MHz.

5.3.9 Fairchild

Advanced Schottky TTL (74F/54F)

Keluarga Fairchild

Advanced Schottky TTL, umumnya dikenal sebagai logika FAST, mirip dengan Keluarga

AS-TTL. Gambar 5.23 menunjukkan skema internal Fairchild Advanced Schottky TTL

5.3.9.1 Fitur KarakteristikFitur karakteristik keluarga ini diringkas sebagai berikut: VIH = 2V; VIL = 0.8V; IIH = 20 A; IIL = 0.6mA; VOH = 2.7V; VOL = 0,5V; IOH = 1mA; IOL = 20mA; VCC = 4.75–5.25V (74F) dan 4.5– 5.5V (54F); penundaan propagasi (resistansi beban 500, kapasitansi beban 50pF dan tegangan operasi penuh dan rentang suhu) = 5.3ns / 7ns (maks.) untuk LOW-to-HIGH dan 6ns / 6.5ns (maks.) untuk HIGH- transisi keluaran ke RENDAH (74AS / 54AS); margin kebisingan kasus terburuk = 0,3V; fanout = 40; ICCH (untuk keempat gerbang) = 2.8mA; ICCL (untuk keempat gerbang) = 10.2mA; kisaran suhu pengoperasian = 0–70 ° C (seri 74F) dan −55 hingga + 125 ° C (seri 54F); kecepatan – daya produk = 10pJ; frekuensi toggle flip-flop maksimum = 125MHz.

5.3.10 Floating and Unused Inputs

5.3.11 Current Transient and Power Supply Decoupling

Komponen:

a. Resistor

Resistor adalah komponen elektronika pasif yang memiliki nilai resistansi atau hambatan tertentu yang berfungsi untuk membatasi dan mengatur arus listrik dalam suatu rangkaian elektronika. Satuan Resistor adalah Ohm (simbol: Ω) yang merupakan satuan SI untuk resistansi listrik. Resitor mempunyai nilai resistansi (tahanan) tertentu yang dapat memproduksi tegangan listrik di antara kedua pin dimana nilai tegangan terhadap resistansi tersebut berbanding lurus dengan arus yang mengalir, berdasarkan persamaan hukum Ohm (V = I.R ).

Rumus dari Rangkaian Seri Resistor: Rtotal = R1 + R2 + R3 + ….. + Rn

Rumus dari Rangkaian paralel Resistor: 1/Rtotal = 1/R1 + 1/R2 + 1/R3 + ….. + 1/Rn

Rumus resistor dengan hukum ohm: R = V/I

Cara menghitung nilai resistor:

Tabel dibawah ini adalah warna-warna yang terdapat di tubuh resistor :

Perhitungan untuk resistor dengan 4 gelang warna :

• Masukkan angka langsung dari kode warna gelang ke-1 (pertama)

• Masukkan angka langsung dari kode warna gelang ke-2

• Masukkan Jumlah nol dari kode warna gelang ke-3 atau pangkatkan angka tersebut dengan 10 (10^n)

• Gelang ke 4 merupakan toleransi dari nilai resistor tersebut

Perhitungan untuk resistor dengan 5 gelang warna :

• Masukkan angka langsung dari kode warna gelang ke-1 (pertama)

• Masukkan angka langsung dari kode warna gelang ke-2

• Masukkan angka langsung dari kode warna gelang ke-3

• Masukkan Jumlah nol dari kode warna gelang ke-4 atau pangkatkan angka tersebut dengan 10 (10^n)

• Gelang ke 5 merupakan toleransi dari nilai resistor tersebut.

b. Transistor NPN

Transistor merupakan alat semikonduktor yang dapat digunakan sebagai penguat sinyal, pemutus atau penyambung sinyal, stabilisasi tegangan, dan fungsi lainnya. Transistor memiliki 3 kaki elektroda, yaitu basis, kolektor, dan emitor. Transistor ini diperumpamakan sebagai saklar, yaitu ketika kaki basis diberi arus, maka arus pada kolektor akan mengalir ke emiter yang disebut dengan kondisi ON. Sedangkan ketika kaki basis tidak diberi arus, maka tidak ada arus mengalir dari kolektor ke emitor yang disebut dengan kondisi OFF. Namun, jika arus yang diberikan pada kaki basis melebihi arus pada kaki kolektor atau arus pada kaki kolektor adalah nol (karena tegangan kaki kolektor sekitar 0,2 - 0,3 V), maka transistor akan mengalami cutoff (saklar tertutup).

Transistor adalah sebuah komponen di dalam elektronika yang diciptakan dari bahan-bahan semikonduktor dan memiliki tiga buah kaki. Masing-masing kaki disebut sebagai basis, kolektor, dan emitor.

• Emitor (E) memiliki fungsi untuk menghasilkan elektron atau muatan negatif.

• Kolektor (C) berperan sebagai saluran bagi muatan negatif untuk keluar dari dalam transistor.

• Basis (B) berguna untuk mengatur arah gerak muatan negatif yang keluar dari transistor melalui kolektor.

Jenis Transistor:

1. Bipolar Junction Transistor (BJT)

Bi artinya dua dan Polar asal kata dari polarity yang artinya polaritas, dengan kata lain bipolar junction transistor (BJT) adalah jenis Transistor yang memiliki dua polaritas yaitu hole (lubang) atau elektron sebagai carier (pembawa) untuk menghantarkan arus listrik. Prinsip dasar konstruksinya disusun seperti dari dua buah dioda yang disambungkan pada kutub yang sama yaitu Anoda dengan anoda sehingga menghasilkan transistor jenis NPN atau Katoda dengan katoda yang menjadi transistor jenis PNP.

2. Unipolar Junction Transistor (UJT

Pada transistor UJT hanya satu polaritas saja yang dijadikan carier/pembawa muatan arus listrik, yaitu elektron saja atau hole/lubangnya saja, tergantung dari jenis transistor UJT tersebut. Karena prinsip kerjanya transistor ini berdasarkan dari efek medan listrik, maka transistor UJT lebih dikenal dengan nama FET (Field Efect Transistor) atau Transistor Efek Medan.

c. Dioda

Dioda adalah komponen yang terbuat dari bahan semikonduktor dan mempunyai fungsi untuk menghantarkan arus listrik ke satu arah tetapi menghambat arus listrik dari arah sebaliknya. Sebuah Dioda dibuat dengan menggabungkan dua bahan semi-konduktor tipe-P dan semi-konduktor tipe-N. Ketika dua bahan ini digabungkan, terbentuk lapisan kecil lain di antaranya yang disebut depletion layer. Ini karena lapisan tipe-P memiliki hole berlebih dan lapisan tipe-N memiliki elektron berlebih dan keduanya mencoba berdifusi satu sama lain membentuk penghambat resistansi tinggi antara kedua bahan seperti pada gambar di bawah ini. Lapisan penyumbatan ini disebut depletion layer.

Ketika tegangan positif diterapkan ke Anoda dan tegangan negatif diterapkan ke Katoda, dioda dikatakan dalam kondisi bias maju. Selama keadaan ini tegangan positif akan memompa lebih banyak hole ke daerah tipe-P dan tegangan negatif akan memompa lebih banyak elektron ke daerah tipe-N yang menyebabkan depletion layer hilang sehingga arus mengalir dari Anoda ke Katoda. Tegangan minimum yang diperlukan untuk membuat dioda bias maju disebut forward breakdown voltage.

Jika tegangan negatif diterapkan ke anoda dan tegangan positif diterapkan ke katoda, dioda dikatakan dalam kondisi bias terbalik. Selama keadaan ini tegangan negatif akan memompa lebih banyak elektron ke material tipe-P dan material tipe-N akan mendapatkan lebih banyak hole dari tegangan positif yang membuat depletion layer lebih besar dan dengan demikian tidak memungkinkan arus mengalir melaluinya. Kondisi ini hanya terjadi pada dioda yang ideal, kenyataannya arus yang kecil tetap dapat mengalir pada bias terbalik dioda.

Dioda dapat dibagi menjadi beberapa jenis:

1. Dioda Penyearah (Dioda Biasa atau Dioda Bridge) yang berfungsi sebagai penyearah arus AC ke arus DC.

2. Dioda Zener yang berfungsi sebagai pengaman rangkaian dan juga sebagai penstabil tegangan. 3. Dioda LED yang berfungsi sebagai lampu Indikator ataupun lampu

4. Dioda Photo yang berfungsi sebagai sensor cahaya. 5. Dioda Schottky yang berfungsi sebagai Pengendali

Karakteristik arus dan tegangan dioda

d. Gerbang Logika OR

e. Gerbang AND

Gerbang AND akan menghasilkan keluaran (Output) Logika 1, jika semua masukan (Input) bernilai Logika 1 dan akan menghasilkan keluaran (Output) Logika 0, jika salah satu dari masukan (Input) bernilai Logika 0.

f. Gerbang NAND

Gerbang NAND akan menghasilkan keluaran (Output) Logika 0, apabila semua masukan (Input) pada Logika 1 dan apabila ada sebuah masukan (Input) yang bernilai Logika 0, maka akan menghasilkan keluaran (Output) Logika 1.

Transistor Gerbang NAND

Secara sederhana, gerbang logika NAND 2 input dapat dibangun menggunakan RTL Resistor-transistor Switch yang terhubung bersama degan input yang terhubung langsung ke basis transistor, dimana transistor harus dalam keadaan cut-off "MATI" untuk keluaran Q.

Gerbang logika NAND dapat menghasilkan fungsi logis yang diinginkan dengan simbol berupa gerbang AND standar dengan tambahan lingkaran (biasa juga disebut sebagai "Gelembung Inversi" pada bagian output yang mana mewakili gerbang NOT) yang disebut sebagai operasi logika NAND.

Jenis Gerbang Logika NAND:

Gerbang NAND 4 Input:

Berdasarkan gambar diatas ekspresi Boolean untuk gerbang NAND 4 input yaitu : Q = A.B.C.D

g. Gerbang NOR

Gerbang NOR akan menghasilkan keluaran (Output) Logika 0, jika salah satu dari masukan (Input) bernilai Logika 1 dan jika ingin mendapatkan keluaran (Output) Logika 1, maka semua masukan (Input) harus bernilai Logika 0.

Jenis Gerbang Logika NOR:

Berdasarkan gambar diatas ekspresi Boolean untuk gerbang NOR 4 input yaitu : Q = A+B+C+D

1. Siapkan semua alat dan bahan.

2. Susun alat dan bahan sesuai gambar rangkaian.

3. Hubungkan semua pin sesuai gambar rangkaian.

4. Jalankan simulasi. Aktifkan logicstate secara bergantian sesuai tabel kebenaran untuk mengetahui logika output gerbang.

Gambar 5.6 menunjukkan skema internal gerbang TTL NAND standar. Ini adalah salah satu dari empat sirkuit 5400/7400, yang merupakan gerbang NAND dua input quad. Sirkuit beroperasi sebagai berikut. Transistor Q1 adalah transistor NPN dua emitor, yang setara dengan dua transistor NPN dengan terminal basis dan emitornya diikat menjadi satu. Dua pemancar adalah dua masukan dari gerbang NAND. Dioda D2 dan D3 digunakan untuk membatasi tegangan input negatif.

Ketika kedua input berada dalam status logika TINGGI seperti yang ditentukan oleh keluarga TTL (minimum VIH = 2 V), arus mengalir melalui dioda persimpangan PN basis-kolektor transistor Q1 ke basis transistor P2. Transistor Q2 dinyalakan ke kondisi saturasi, akibatnya transistor Q3 dalam posisi OFF dan transistor Q4 dalam posisi ON. Ini menghasilkan logika LOW pada output, dengan VOL maksimum 0,4 V. ketika tenggelam arus 16 mA dari beban eksternal yang diwakili oleh input fungsi logika yang digerakkan oleh output. Tindakan penenggelaman arus ditunjukkan pada Gambar 5.7 (a). Transistor Q4 juga disebut sebagai transistor saat ini-tenggelam atau pull-down, untuk alasan yang jelas. Diode D1 digunakan untuk mencegah transistor Q3 berjalan bahkan arus dalam jumlah kecil saat output LOW. Ketika outputnya LOW, Q4 dalam keadaan jenuh dan Q3 akan berjalan sedikit jika D1 tidak ada. Juga, arus input IIH dalam keadaan HIGH tidak lain adalah arus bocor dioda persimpangan bias balik dan biasanya 40 A.

Ketika salah satu dari

dua input atau kedua input berada dalam status logika RENDAH, wilayah

basis-emitor dari Q1 mengalirkan arus, mendorong Q2 untuk memutus dalam proses.

Ketika Q2 dalam keadaan cut-off, Q3 didorong ke konduksi dan Q4 ke cut-off. Ini

menghasilkan output logika TINGGI dengan VOH (min.) = 2,4 V dijamin untuk

tegangan suplai minimum VCC dan arus sumber 400 A. Tindakan sumber saat ini

ditunjukkan pada Gambar 5.7 (b). Transistor Q3 juga disebut sebagai transistor

sumber arus atau pull-up. Juga, IIL arus input level-RENDAH, yang diberikan

oleh (VCC − VBE1 / R1, adalah 1,6 mA (maks.) Untuk VCC maksimum.

Gambar 5.8 menunjukkan skema internal gerbang NOT (inverter) dalam keluarga TTL standar. Itu skema yang ditampilkan adalah salah satu dari enam inverter dalam inverter hex (tipe 7404/5404). Internal Skema sama dengan yang ada pada gerbang NAND kecuali bahwa transistor input adalah single normal emitor NPN transistor, bukan multi-emitor. Sirkuitnya cukup jelas.

Gambar 5.9 menunjukkan skema internal gerbang NOR dalam keluarga TTL standar. Skema yang ditunjukkan adalah salah satu dari empat gerbang NOR dalam gerbang NOR empat masukan dua (tipe 7402/5402). Disisi input ada dua transistor terpisah sebagai pengganti transistor multi-emitor dari gerbang NAND. Input diumpankan ke pemancar dari dua transistor, kolektor yang lagi-lagi memberi makan basis dua transistor dengan terminal kolektor dan emitor diikat menjadi satu. Nilai resistansi yang digunakan sama dengan yang digunakan dalam kasus gerbang NAND. Tahap keluaran juga merupakan tiang totem yang sama tahap keluaran. Sirkuitnya cukup jelas. Satu-satunya kondisi input di mana transistor Q3 dan Q4 tetap dalam cut-off, sehingga mendorong Q6 ke cut-off dan Q5 ke konduksi, adalah kondisi ketika kedua input berada dalam keadaan logika LOW. Output dalam kasus seperti itu adalah logika TINGGI. Untuk semua kondisi input lainnya, baik Q3 atau Q4 akan berjalan, mengarahkan Q6 ke saturasi dan Q5 ke cut-off, menghasilkan logika RENDAH pada output.

Gambar 5.10 menunjukkan skema internal gerbang AND dalam keluarga TTL standar. Skema yang ditampilkan adalah salah satu dari empat gerbang AND dalam gerbang AND dua masukan quad (tipe 7408/5408). Dalam urutan untuk menjelaskan bagaimana pengaturan skema ini berperilaku sebagai gerbang AND, kita akan mulai dengan menyelidiki kondisi input yang akan menghasilkan output HIGH. Output HIGH menyiratkan Q6 berada di cut-off dan Q5 berada dalam konduksi. Ini dapat terjadi hanya jika Q4 di-cut-off. Transistor Q4 dapat berada dalam kondisi cut-off hanya ketika Q2 dan Q3 dalam konduksi. Ini hanya mungkin jika kedua input berada dalam status logika TINGGI. Sekarang mari kita lihat apa yang terjadi ketika salah satu dari dua input didorong ke status LOW. Ini mendorong Q2 dan Q3 ke kondisi cut-off, yang memaksa Q4 dan kemudian Q6 ke saturasi dan Q5 ke cut-off.

Gambar 5.11 menunjukkan skema internal gerbang OR dalam keluarga TTL standar. Skema yang ditampilkan adalah salah satu dari empat gerbang OR dalam gerbang OR dua input quad (tipe 7432/5432). Kami akan mulai dengan menyelidiki kondisi input yang akan menyebabkan output LOW. Output yang RENDAH menuntut Q8 jenuh dan Q7 yang terputus. Hal ini pada gilirannya membutuhkan Q6 berada dalam saturasi dan Q5, Q4 dan Q3 harus di-cut-off. Ini hanya mungkin jika Q1 dan Q2 berada dalam saturasi. Artinya, kedua input berada dalam status logika LOW. Ini memverifikasi salah satu entri tabel kebenaran dari gerbang OR. Sekarang mari kita lihat apa yang terjadi ketika salah satu dari dua input didorong ke status TINGGI. Ini mendorong salah satu dari dua transistor Q3 dan Q4 ke saturasi, yang memaksa Q5 ke saturasi dan Q6 ke cut-off. Ini mendorong Q7 ke konduksi dan Q8 ke cut-off, menghasilkan output logika TINGGI.

Gambar 5.12 menunjukkan skema internal gerbang EX-OR dalam keluarga TTL standar. Skema yang ditampilkan adalah salah satu dari empat gerbang EX-OR dalam gerbang EX-OR dua input (tipe 7486/5486). Kami akan mencatat persamaan antara sirkuit ini dan dari gerbang OR. Satu-satunya elemen baru adalah pasangan transistor Q7 dan Q8 yang saling berhubungan. Kita akan melihat bahwa, ketika kedua inputnya TINGGI atau RENDAH, baik Q7 dan Q8 tetap terputus. Dalam kasus input berada dalam status logika TINGGI, terminal basis dan emitor dari kedua transistor ini tetap berada di dekat potensial ground. Jika input dalam keadaan RENDAH, terminal basis dan emitor dari kedua transistor ini tetap berada di dekat VCC. Hasilnya adalah melakukan Q9 dan Q11 dan nonconducting Q10, yang menghasilkan keluaran RENDAH. Ketika salah satu input TINGGI, baik Q7 atau Q8 bekerja. Transistor Q7 bekerja ketika input B TINGGI, dan transistor Q8 berjalan ketika input A TINGGI. Melakukan Q7 atau Q8 mematikan Q9 dan Q11 dan menyalakan Q10, menghasilkan output TINGGI. Ini menjelaskan bagaimana rangkaian ini berperilaku sebagai gerbang EX-OR.

Gambar 5.13 menunjukkan skema internal dari gerbang AND-OR-INVERT atau AND-NOR dua-lebar, dua input. Skema yang ditampilkan adalah salah satu dari dua gerbang dalam gerbang AND-ORINVERT dua lebar, dua input (tipe 7450/5450). Dua transistor masukan multi-emitor Q1 dan Q2 menyediakan ANDing dari masing-masing masukannya. Pembagi drive yang terdiri dari Q3, Q4, R3 dan R4 menyediakan fungsi OR. Tahap keluaran memberikan inversi. Jumlah pemancar di setiap transistor masukan menentukan jumlah literal di setiap minterms dalam jumlah keluaran produk ekspresi Boolean. Seberapa lebar gerbang akan ditentukan oleh jumlah transistor input, yang juga sama dengan jumlah transistor pemisah drive.

5.14 menunjukkan skema internal gerbang NAND dengan keluaran kolektor terbuka. Skema yang ditampilkan adalah salah satu dari empat gerbang dari NAND dua input quad (tipe 74/5401). Keuntungan dari keluaran kolektor terbuka adalah bahwa keluaran dari gerbang yang berbeda dapat dihubungkan bersama, menghasilkan AND dari keluarannya. Operasi WIRE-AND telah dibahas pada Bab 4 tentang gerbang logika. Dapat disebutkan di sini bahwa output perangkat TTL kutub-totem tidak dapat diikat bersama. Meskipun output terikat umum mungkin akhirnya menghasilkan ANDing dari output individu, koneksi seperti itu tidak praktis

Pada gambar 5.15, di mana keluaran dari dua gerbang TTL keluaran kutub-totem telah diikat menjadi satu. Mari kita asumsikan bahwa output dari salah satu gerbang, katakanlah gate-2, adalah RENDAH, dan output dari gerbang lainnya adalah TINGGI. Hasilnya adalah arus yang relatif lebih berat mengalir melalui Q31 dan Q42. Arus ini, dengan urutan 50–60 mA, melebihi peringkat IOL (maks.) Q42. Ini pada akhirnya dapat menyebabkan kedua transistor rusak. Bahkan jika mereka bertahan, VOL (maks.) Dari Q42 tidak lagi dijamin. Mengingat hal ini, meskipun gerbang TTL keluaran kutub-totem tidak terikat bersama, korslet keluaran yang tidak disengaja tidak dikesampingkan. Dalam kasus seperti itu, kedua perangkat kemungkinan besar rusak. Dalam kasus perangkat kolektor terbuka, disengaja atau tidak disengaja, kekurangan output menghasilkan ANDing output tanpa risiko kerusakan atau spesifikasi kinerja yang terganggu.

Gambar 5.16 menunjukkan skema internal tipikal dari inverter tristate dengan input aktif TINGGI. Rangkaian tersebut berfungsi sebagai berikut. Ketika input pengaktifannya TINGGI, itu membiaskan dioda D1 dan juga menerapkan logika TINGGI pada salah satu pemancar dari transistor input Q1. Sirkuit berperilaku seperti inverter. Saat input pengaktifan LOW, dioda D1 menjadi bias maju. A RENDAH memungkinkan input memaksa Q2 dan Q4 untuk memotong. Juga, D1 bias maju memaksa Q3 untuk memotong. Dengan kedua transistor keluaran di cut-off, keluaran pada dasarnya adalah rangkaian terbuka dan dengan demikian menghadirkan impedansi keluaran yang tinggi.

Gambar 5.17 menunjukkan skema internal gerbang TTL NAND daya rendah. Sirkuit yang ditampilkan adalah salah satu dari empat gerbang di dalam quad dua input NAND (tipe 74L00 atau 54L00). Rangkaian, seperti yang dapat kita lihat, sama dengan yang ada pada gerbang TTL NAND standar kecuali untuk peningkatan nilai resistansi dari resistor berbeda yang digunakan dalam rangkaian. Nilai resistansi yang meningkat menyebabkan disipasi daya yang lebih rendah.

Gambar 5.18 menunjukkan skema internal gerbang TTL NAND daya tinggi. Sirkuit yang ditampilkan adalah salah satu dari empat gerbang di dalam quad dua input NAND (tipe 74H00 atau 54H00). Rangkaian, seperti yang dapat kita lihat, hampir sama dengan yang ada pada gerbang NAND TTL standar kecuali untuk kombinasi transistor Q3-dioda D1 dalam tingkat keluaran kutub-totem yang telah diganti dengan pengaturan Darlington yang terdiri dari Q3, Q5 dan R5. Susunan Darlington melakukan pekerjaan yang sama seperti dioda D1 dalam susunan tiang totem konvensional. Ini memastikan bahwa Q5 tidak bekerja sama sekali ketika outputnya RENDAH. Nilai resistansi yang menurun dari berbagai resistor yang digunakan dalam rangkaian menyebabkan disipasi daya yang lebih tinggi.

Gambar 5.19 menunjukkan skema internal gerbang Schottky TTL NAND. Sirkuit yang ditampilkan adalah salah satu dari empat gerbang di dalam quad dua input NAND (tipe 74S00 atau 54S00). Sirkuit, seperti yang bisa kita lihat, hampir sama dengan gerbang NAND TTL berdaya tinggi. Transistor yang digunakan dalam rangkaian adalah semua transistor Schottky dengan pengecualian Q5. Schottky Q5 tidak akan berguna, dengan Q4 sebagai transistor Schottky. Transistor Schottky tidak lain adalah transistor bipolar konvensional dengan dioda Schottky yang terhubung antara basis dan terminal kolektornya. Dioda Schottky dengan sambungan logam-semikonduktornya tidak hanya lebih cepat tetapi juga menawarkan penurunan tegangan maju yang lebih rendah sebesar 0,4V dibandingkan 0,7V untuk dioda sambungan P – N untuk nilai arus maju yang sama. Kehadiran dioda Schottky tidak memungkinkan transistor mengalami saturasi yang dalam. Saat tegangan kolektor transistor cenderung turun di bawah sekitar 0,3V, dioda Schottky menjadi bias maju dan melewati bagian dari arus basis yang melewatinya. Dengan demikian, tegangan kolektor tidak diizinkan untuk mencapai nilai saturasi 0,1V dan dijepit sekitar 0,3V. Sementara konsumsi daya gerbang Schottky TTL hampir sama dengan gerbang TTL berdaya tinggi karena nilai resistor yang hampir sama yang digunakan di sirkuit, Schottky TTL menawarkan kecepatan yang lebih tinggi karena penggunaan Schottky transistor.

Gambar 5.20 menunjukkan skema internal gerbang NAND Schottky TTL berdaya rendah. Sirkuit yang ditunjukkan adalah salah satu dari empat gerbang di dalam quad dua input NAND (tipe 74LS00 atau 54LS00). Kita dapat melihat nilai resistor R1 dan R2 yang meningkat secara signifikan yang digunakan untuk mencapai konsumsi daya yang lebih rendah. Konsumsi daya yang lebih rendah, tentu saja, terjadi dengan mengorbankan kecepatan yang berkurang atau penundaan propagasi yang meningkat. Resistor R3 dan R5, yang terutama mempengaruhi kecepatan, belum dinaikkan dalam proporsi yang sama sehubungan dengan nilai-nilai yang sesuai yang digunakan dalam Schottky TTL sebagai resistor R1 dan R2. Itulah sebabnya, meskipun daya rendah Schottky TTL menarik arus suplai maksimum rata-rata 3 mA (untuk keempat gerbang) dibandingkan 26 mA untuk Schottky TTL, penundaan propagasi adalah 15 ns di LS-TTL dibandingkan 5 ns untuk S-TTL. Dioda D3 dan D4 mengurangi penundaan propagasi HIGH-to-LOW. Sementara D3 mempercepat mematikan Q4, D4 menurunkan arus dari beban. Perbedaan nyata lainnya dalam skema internal dari Schottky TTL NAND daya rendah dan Schottky TTL NAND adalah penggantian transistor input multi-emitor dari Schottky TTL dengan dioda D1 dan D2 dan resistor R1. Dioda persimpangan pada dasarnya menggantikan dua persimpangan basis-emitor dari transistor input multi-emitor Q1 dari Schottky TTL NAND (Gbr. 5.19). Alasan untuk melakukannya adalah karena dioda Schottky dapat dibuat lebih kecil dari transistor dan oleh karena itu akan memiliki kapasitansi parasit yang lebih rendah. Juga, karena Q1 dari LS-TTL (Gbr. 5.20) tidak dapat jenuh, muatan basisnya tidak perlu dilepas dengan transistor pertemuan bipolar.

Gambar 5.21 menunjukkan skema internal gerbang NAND Schottky TTL daya rendah tingkat lanjut. Rangkaian yang ditunjukkan adalah salah satu dari empat gerbang di dalam quad dua input NAND (tipe 74ALS00 atau 54ALS00) Transistor input multi-emitor digantikan oleh dua transistor PNP Q1A dan Q1B. Dioda D1A dan D1B memberikan penjepitan input ke ekskursi negatif. Penyangga yang ditawarkan oleh Q1A atau Q1B dan Q2 mengurangi arus input level RENDAH dengan faktor (1 + hFE dari Q1A. Tegangan output level TINGGI ditentukan terutama oleh VCC, transistor Q6 dan Q7 dan resistor R4 dan R7 dan biasanya (VCC − 2) V. Tegangan output level rendah ditentukan oleh karakteristik turn-on Q5. Transistor Q5 mendapatkan penggerak basis yang cukup melalui R3 dan Q3 konduksi yang terminal dasarnya digerakkan oleh Q2 konduksi setiap kali salah satu atau keduanya input TINGGI Transistor Q4 menyediakan turn-off aktif untuk Q5.

Gambar 5.22 menunjukkan skema internal gerbang Schottky TTL NAND tingkat lanjut. Sirkuit yang ditampilkan adalah salah satu dari empat gerbang di dalam quad dua input NAND (tipe 74AS00 atau 54AS00). Fitur yang menonjol dari ALS-TTL dan AS-TTL telah dibahas panjang lebar di paragraf sebelumnya. Seperti yang terlihat jelas dari skema rangkaian internal gerbang AS-TTL NAND, ia memiliki beberapa rangkaian tambahan yang tidak ditemukan di perangkat ALS-TTL. Ini ditambahkan untuk meningkatkan throughput perangkat keluarga AS-TTL. Transistor Q10 menyediakan jalur pelepasan untuk kapasitansi basis-kolektor Q5. Dengan tidak adanya Q10, tegangan yang naik melintasi arus gaya keluaran ke basis Q5 melalui kapasitansi basis-kolektor, sehingga menyebabkannya menyala. Transistor Q10 menyala melalui D9, sehingga transistor Q5 dalam keadaan cut-off.

Gambar 5.23 menunjukkan skema internal gerbang NAND Fairchild Advanced Schottky TTL. Sirkuit yang ditampilkan adalah salah satu dari empat gerbang di dalam quad dua input NAND (tipe 74F00 atau 54F00). Jenis input DTL dengan konfigurasi pengikut emitor pada Q1 menyediakan penggerak dasar yang baik ke Q2. Konfigurasi 'Miller killer' yang terdiri dari dioda varactor D7, transistor Q6 dan komponen terkait mempercepat transisi LOW-to-HIGH. Selama transisi LOW-to-HIGH, tegangan pada terminal emitor Q3 mulai naik sementara Q5 masih berjalan. Dioda Varactor D7 bekerja, sehingga memasok arus basis ke Q6. Sebuah Q6 konduksi menyediakan jalur pelepasan untuk muatan yang disimpan dalam kapasitansi basis-kolektor dari Q5, sehingga mempercepat pematiannya.

Ketika inputnya TINGGI, persimpangan basis-emitor input bias balik dan arus yang mengalir ke input adalah arus bocor dioda bias balik. Dioda input akan bias terbalik bahkan ketika terminal input dibiarkan tidak terhubung atau mengambang, yang menyiratkan bahwa input mengambang berperilaku seolah-olah ada logika TINGGI yang diterapkan padanya. Sebagai pemikiran awal, kita mungkin cenderung percaya bahwa itu seharusnya tidak membuat perbedaan jika kita membiarkan input yang tidak digunakan dari gerbang NAND dan AND sebagai mengambang, karena logika TINGGI seperti perilaku input mengambang tidak membuat perbedaan pada perilaku logis dari gerbang. , seperti yang ditunjukkan pada Gambar 5.24 (a) dan (b). Meskipun demikian, sangat disarankan agar input gerbang AND dan gerbang NAND yang tidak digunakan dihubungkan ke input logika TINGGI [Gbr. 5.24 (c)] karena input mengambang berperilaku sebagai antena dan dapat menangkap sinyal gangguan dan gangguan yang menyimpang, sehingga menyebabkan gerbang berfungsi tidak semestinya. Resistansi 1 k terhubung untuk melindungi input dari lonjakan arus yang disebabkan oleh lonjakan apa pun pada saluran catu daya. Lebih dari satu input yang tidak digunakan (hingga 50) dapat berbagi resistansi 1 k yang sama, jika perlu. Dalam kasus gerbang OR dan NOR, input yang tidak digunakan dihubungkan ke ground (logika LOW), seperti yang ditunjukkan pada Gambar 5.25 (c), untuk alasan yang jelas. Input floating atau input yang terikat ke logika TINGGI dalam hal ini menghasilkan logika permanen TINGGI (untuk gerbang OR) dan RENDAH (untuk gerbang NOR) pada output seperti yang ditunjukkan pada Gambar 5.25 (a) dan (b) masing-masing. Solusi alternatif ditunjukkan pada Gambar 5.25 (d), di mana input yang tidak digunakan telah diikat ke salah satu input yang digunakan. Solusi ini bekerja dengan baik untuk semua gerbang, tetapi kita harus menyadari fakta bahwa kemampuan kipas keluar dari keluaran yang menggerakkan masukan yang terikat tidak terlampaui. Jika kita mengingat skema rangkaian internal gerbang AND dan gerbang NAND, kita akan menghargai bahwa, ketika lebih dari satu input diikat bersama, beban input, yaitu, arus yang ditarik oleh input yang diikat dari output gerbang penggerak, di HIGH status adalah n kali pembebanan satu input (Gbr. 5.26); n adalah jumlah input yang diikat. Ketika output RENDAH, pembebanan input sama dengan input tunggal. Alasan untuk ini adalah bahwa, dalam keadaan input RENDAH, arus yang mengalir keluar dari gerbang ditentukan oleh resistansi R1, seperti yang ditunjukkan pada Gambar 5.27. Namun, hal yang sama tidak berlaku dalam kasus gerbang OR dan NOR, yang tidak menggunakan transistor masukan multi-emitor dan sebaliknya menggunakan transistor masukan terpisah.

Seperti yang ditunjukkan pada Gambar 5.28. Dalam hal ini, pembebanan masukan adalah n kali pembebanan masukan tunggal untuk status TINGGI dan RENDAH.

Gambar 5.29 mengilustrasikan ketika output berubah dari RENDAH ke TINGGI, ada sedikit waktu ketika kedua transistor berjalan karena transistor pull-up Q3 telah menyala dan transistor pull-down Q4 belum keluar dari kejenuhan. Selama fraksi waktu yang kecil ini, terjadi peningkatan arus yang ditarik dari suplai; ICCL mengalami lonjakan positif sebelum menetap ke ICCH yang biasanya lebih rendah. Kehadiran kapasitansi C yang menyimpang di output karena kapasitansi kabel yang menyimpang atau pemuatan kapasitansi dari rangkaian yang diberi makan juga menambah masalah. Masalah lonjakan tegangan pada saluran catu daya biasanya diatasi dengan menghubungkan kapasitor bernilai kecil, induktansi rendah, frekuensi tinggi antara terminal VCC dan ground. Merupakan praktik standar untuk menggunakan kapasitor keramik 0,01 atau 0,1 F dari VCC ke ground. Kapasitor ini juga dikenal dengan nama kapasitor decoupling catu daya, dan disarankan untuk menggunakan kapasitor terpisah untuk setiap IC. Kapasitor decoupling dihubungkan sedekat mungkin ke terminal VCC, dan kabelnya dijaga seminimal mungkin untuk meminimalkan induktansi timbal. Selain itu, satu kapasitor bernilai relatif besar dalam kisaran 1–22 F juga dihubungkan antara VCC dan arde pada setiap kartu sirkuit untuk menangani fluktuasi tegangan frekuensi rendah di jalur catu daya.

5.6

5.9

5.10

5.12

5.13

5.145.165.175.185.195.205.215.225.235.24-5.255.26-5.28

File Simulasi Proteus 5.24-5.25

File Simulasi Proteus 5.26-5.28

Datasheet Dioda Varactor ZC830A

Daatasheet Dioda Rectifier 1N4001

Download Datasheet Dioda Schottky 10BQ040

1. Berdasarkan Gambar 5.30. Tentukan arus yang bersumber dari gerbang 1 ketika outputnya HIGH dan turun ketika outputnya LOW. Semua gerbang berasal dari keluarga TTL standar, dengan IIH = 40uA dan IIL = 1,6mA.

Solultion:

- Ketika outputnya TINGGI, input dari semua gerbang menarik arus satu per satu.

- Oleh karena itu, faktor pembebanan input = ekuivalen dengan input tujuh gerbang = 7 × 40 A = 280 A.

- Arus yang bersumber dari output gerbang 1 = 280 A.

- Ketika outputnya RENDAH, input korsleting gerbang AND dan gerbang NAND menawarkan beban yang sama dengan input tunggal karena transistor multi-emitor pada input gerbang. Input gerbang OR dan NOR menarik arus secara individual karena penggunaan transistor terpisah pada input gerbang.

- Oleh karena itu, faktor pembebanan input = ekuivalen dengan input lima gerbang = 5 × 1,6 = 8 mA.

- Arus yang ditenggelamkan oleh gerbang 1 keluaran = 8 mA.

2. Berdasarkan diagram logika pada Gambar 5.31. Gerbang 1 dan gerbang 4 termasuk dalam keluarga TTL standar, sedangkan gerbang 2 dan gerbang 3 masing-masing milik keluarga Schottky TTL dan keluarga Schottky TTL berdaya rendah. Tentukan apakah kapabilitas fan-out gerbang 1 terlampaui. Data yang relevan untuk tiga keluarga logika diberikan pada Tabel 5.1.

Solution:

- Saat input HIGH

- kemampuan sumber keluaran gerbang 1 = 400 A;

- persyaratan input gerbang 2 = 50 × 4 = 200 A;

- persyaratan input gerbang 3 = 20 × 2 = 40 A;

- persyaratan input gerbang 4 = 40 × 4 = 160 A;

- total kebutuhan arus input = 400 A;

- oleh karena itu, fan-out tidak terlampaui dalam status TINGGI.

- Saat input LOW

- kemampuan tenggelam keluaran gerbang 1 = 16 mA;

- persyaratan tenggelamnya gerbang 2 input = 2 mA;

- persyaratan tenggelamnya masukan gerbang 3 = 0,4 × 2 = 0,8 mA;

- persyaratan tenggelamnya gerbang 4 input = 1,6 mA;

- total kebutuhan arus input = 4,4 mA;

- karena keluaran dari gerbang 1 memiliki kemampuan penurunan arus sebesar 16 mA, kemampuan kipas keluar juga tidak terlampaui dalam keadaan RENDAH.

1. Berapa banyak input dari Low-Power Schottky TTL NAND yang dapat digerakkan secara andal dari satu output dari Schottky TTL NAND, diketahui spesifikasi relevan berikut untuk perangkat dari dua subfamili TTL:

Schottky TTL: IOH = 1,0 mA; IIH = 0,05 mA; IOL = 20,0 mA; IIL = 2.0 mALow-Power Schottky TTL: IOH = 0.4 mA; IIH = 0,02 mA; IOL = 8,0 mA; IIL = 0,4 mA

Solution:

Fan-out HIGH = 1mA/0.02mA = 50

Fan-out LOW = 20mA/0.4mA = 50

2. Hasil akhir = 50Berdasarkan diagram logika pada Gambar 5.66. Tentukan arus yang bersumber dari gerbang NAND ketika outputnya TINGGI dan juga arus yang turun ketika outputnya RENDAH, diketahui bahwa IIH (gerbang AND) = 0,02 mA, IIL (gerbang AND) = 0,4 mA, IIH (OR gerbang) = 0,04 mA, IIL (gerbang OR) = 1,6 mA, IOH (gerbang NAND) = 1,0 mA, IOL (gerbang NAND) = 20,0 mA.

Solution:

Arus HIGH = 2*IIH(AND) + IIH(OR) = 0.04 + 0.04 = 0.08mA

Arus LOW = IIL(AND) + IIL(OR) = 0.4 + 1.6 = 2.0mA

1. Gerbang yang ditunjukkan oleh gambar berikut adalah...

a. OR

b. AND

c. NOT

d. NAND

2. Berdasarkan rangkaian berikut, apabila kedua input (logicstate) berlogika 1 maka...

b. Output berlogika 1 dan Q3 aktif

c. Output berlogika 0 dan Q3 aktif.

Tidak ada komentar:

Posting Komentar